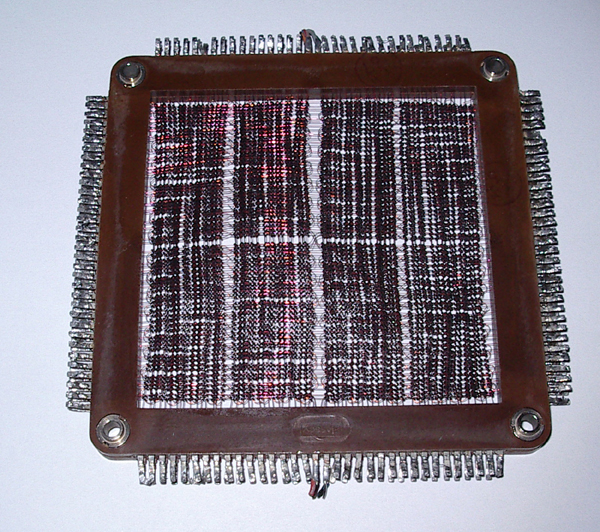

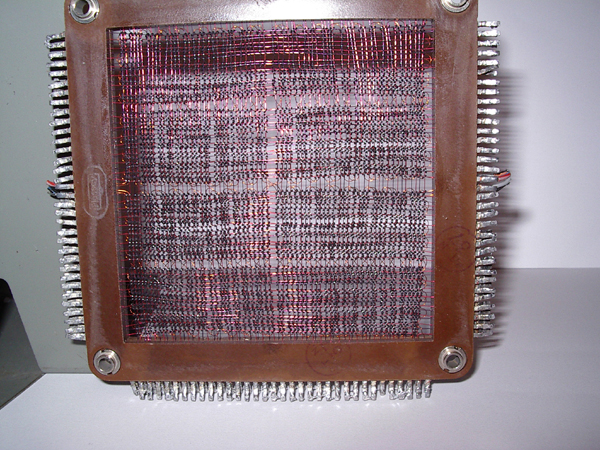

The Atlas core memory was made by Plessey in these square ferrite core memory planes. Each side of the Bakelite frame had about 68 contacts on the outside. The memory itself consisted of a grid of thin wires with each junction containing a ferrite core. The size of the board is about 12 centimetres square and contained about 64 by 64 cores (bits).