The first phase of a new initiative in the engineering applications of transputers was launched in May. This £3.5 million programme, which is intended to run for four years, is being jointly funded by SERC's Engineering Board and the Department of Trade and Industry. Joint funding means that both industry and institutions of higher education can take part.

The aims of the programme are:

Through the programme, which is being coordinated at the Rutherford Appleton Laboratory, participants are offered access to appropriate transputer hardware, software and expertise through a loan pool and through four support centres to be established at academic sites.

The initiative arose from the recommendations of a working group of the Engineering Board's Computing Facilities Committee, chaired by Professor D Lewin of Sheffield University, which reported in 1986.

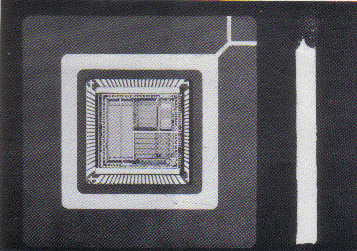

The transputer is a new super-microcomputer on a single silicon chip, designed and manufactured in Britain by Inmos Ltd. It is the first discrete silicon device in the world to provide an effective vehicle for parallel processing (the simultaneous application of many processors to the same problem). This is a technique which promises computer systems with a price:performance ratio several orders of magnitude better than those available today. Future parallel processors will greatly reduce the cost of tasks performed by today's machines and will solve important problems which are not feasible at present. Britain enjoys a world lead in parallel processing techniques but there is a narrow window of opportunity in which to exploit this lead.

For further information on the Engineering Applications of Transputers Initiative, contact Dr M R Jane, at Rutherford Appleton Laboratory, telephone Abingdon (0235) 445408.