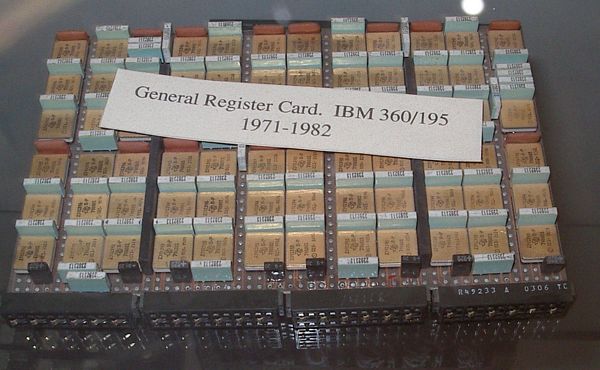

The 360/195 used monolithic integrated ECL circuits for the arithmetic and logic operations in the central processor combined with the 32 Kbyte high speed buffer memory. Each silicon memory chip was about 0.125 inches square and consisted of 664 transistors and diodes etc. Each memory chip contained from two to four circuits, stored 64 bits of data, and were mounted on a 0.5 inch ceramic substrate. The monolithic circuits transmitted signals in 3-5 nanoseconds.