The original paper had every paragraph and list item separately numbered. These have been omitted except on the top two levels. References are now numbered [1] etc.

Le caractère fondamental de la machine de l'Institut Blaise Pascal est d'être machine du type parallèle. Les particularités propres à ce type de machines leur confèrent divers avantages, et la machine est étudiée de manière à tirer le meilleur parti de ces particularités. Je voudrais montrer, par quelques exemples, dans quels sens se poursuivent nos recherches, et indiquer quelques uns des résultats obtenus.

La raison des combinaisons de circuits auxquels nous sommes arrêtés apparaîtra mieux à la clarté d'une analyse de la suite des opérations élémentaires concourant à réaliser "en parallèle" les opérations arithmétiques fondamentales.

La representation d'un nombre exige un organe de chiffrage pour chaque ordre binaire.

Par exemple, si la machine est construite pour représenter les nombres de 0 à 26 , il faudra 6 organes élémentaires, schématisés sur la fig.1, où on suppose inscrit le nombre IIII00.

Chacun des organes de chiffrage peut prendre deux états physiques représentant, le premier, le chiffre 0, le second, le chiffre I.

L'ensemble de ces organes constitue un chiffreur (register): pour effectuer la répresentation d'un nombre sur un chiffreur, pour supprimer le nombre représenté sur un chiffreur, ou, enfin, pour transférer ce nombre à un autre chiffreur, il faut disposer d'organes particuliers:

L'inscription successive de deux nombres dans le même chiffreur fait apparaître la somme de ces deux nombres si le chiffreur est complété par un dispositif qui permette, lorsque I est inscrit après I dans un ordre binaire, de remplacer I par 0 et d'ajouter I dans l'ordre binaire immédiatement supérieur.

Ce dispositif est appelé un reporteur (carry over device).

Mais le jeu des reports peut augmenter le nombre des chiffres des deux nombres.

Par exemple, IIII00 + I0I = I00000I.

Il faut donc munir le chiffreur de quelques éléments supplémentaires. Nous les appellerons éléments de report. Dans les figures qui vont suivre, nous supposerons qu'il y a un seul élément de report.

Un chiffreur muni d'un reporteur sera appelé un totalisateur (adding device).

La plupart des machines à calculer font la soustraction par la méthode des compléments, qui consiste à remplacer la soustraction d'un nombre par l'addition de son complément.

[2] Le complément d'un nombre binaire s'obtient en remplaçant 0 par I et I par 0 de gauche à droite jusqu'au dernier chiffre I, qui est conservé ainsi que les 0 qui le suivent.

Par exemple, dans un chiffreur à 7 éléments, le complément de I0I0 s'écrit III0II0; la soustraction IIII00 - I0I0 se présente ainsi:

Le dernier report à gauche, qui donnerait un chiffre I dans le huitième élément ne pent pas être représenté; c'est pourquoi le résultat représenté sur le totalisateur est exact.

Mais si l'on avait proposé à la machine l'opération IIII00 + III0II0, on aurait obtenu II00I0, ce qui est faux.

Il faut, pour éviter ce cas, soit prendre garde que le totalisateur ne peut recevoir que des nombres de 6 chiffres, (et ceci met en relief le rôle exceptionnel de l'élément de report placé au 7e rang), soit conserver le report du 7e rang vers la gauche, et l'utiliser pour annoncer que la machine a été appelée à faire une opération impossible.

[1] Mais il est plus avantageux d'utiliser ce report pour représenter de façon permanente le signe du nombre calculé par le totalisateur, et rendre ainsi ce dernier algébrique.

Si l'on convient de placer à gauche du chiffreur un élément supplémentaire, appelé chiffreur de signe (sign register), et de représenter sur cet élément le signe + par le chiffre 0, et le signe - par le chiffre I, la soustraction de la figure 3 se présente comme suit:

Le zero du chiffreur de signe montre que le résultat est positif.

L'opération I0I0 - IIII00 = - II00I0 se présenterait ainsi:

On voit que la répresentation normale d'un nombre négatif sur un chiffreur parallèle est formée du chiffre I dans le chiffreur de signe et du complément du nombre (et non, comme l'on aurait pu le présumer, du signe et de la représentation du nombre positif qui constitue le module du nombre).

Un totalisateur muni d'un chiffreur de signe est appelé totalisateur algébrique.

Le cas du paragraphe [1], donne, dans un totalisateur algébrique, l'effet que voici:

Le résultat est encore faux.

Pour l'éviter, on peut, soit prendre garde, dans le programme, de ne pas inscrire de nombres de capacité trop grande, soit, mieux, prévoir un signal d'alarme, avertissant lorsque les signes des nombres donnés sont les mêmes et que le signe du résultat est différent.

Nous l'appellerons l'alarme de capacité (capacity alarm).

Enfin, il est à remarquer que la règle de formation du couplément est assez compliquée ([2]).

Or, on peut replacer le complément par le permuté (permutation), obtenu en remplaçant tous les 0 par des I et tous les I par des 0, ce qui constitue une règle d'application aisée, à condition de munir le totalisateur d'un report allant du chiffreur de signe à l'ordre binaire le plus faible.

Le schéma se présente ainsi:

Nous appellerons report sans fin (round carry over) le dispositif qui vient d'être décrit.

Remarquons que l'analyse du fonctionnement deétaillé d'un totalisateur parallèle dans l'addition et la soustraction, met en évidence des particularités qui ne se présentent pas dans l'application des règles arithmétiques usuelles des opérations. Nous en trouverons de nouvelles dans les autres opérations.

La multiplication peut être réalisée selon le processus expliqué sur l'exemple suivant: I0I0 × II0.

Le multiplicande I0I0 est inscrit sur un chiffreur M; le multiplicateur II0, sur un chiffreur X; le produit se forme dans un totalisateur P. Un régulateur (clock) règle la suite des opérations:

(Les doubles traits, représentent un transfert; les traits simples, un ordre; les nombres dans un cercle le rang des opérations dans le temps).

(1): Le chiffre I dans l'élément de gauche de X commande le transfert de M à P.

(2): Le régulateur commande le déplacement du nombre figuré dans X d'un pas vers la gauche, et le déplacement du nombre figuré dans M d'un pas vers la droite.

(3): identique à (1).

(4): identique à (2).

(5): Le chiffre 0 dans l'élément de gauche de X ne commande aucun transfert.

(6): Le régulateur arrête l'operation.

La multiplication arithmétique demande donc:

La multiplication algébrique peut s'effectuer de deux facons: ou bien on considère le chiffre inscrit dans le chiffreur de signe comme un véritable chiffre faisant partie de la représentation du nombre, ou bien on traite séparément les modules (comme il vient d'être dit) et les signes, selon la règle des signes, qui revient d'ailleurs, à additionner les signes sans faire de report, dans le cas de I + I.

Pour une raison qui apparaîtra bientôt clairement, nous préférons la seconde méthode.

Cette méthode nécessite:

Un dispositif de permutation des nombres qui doivent entrer dans X et M. Nous lui conserverons le nom d'overdraft, utilisé dans les machines mécaniques.

Un totalisateur sans report pour la totalisation des signes. Nous l'appellerons le calculateur de signe.

La division peut être réalisée, dans une machine parallèle, selon un processus très simple et très rapide, expliqué sur l'exemple suivant: IIII00 : I0I0.

Le dividende IIII00 est inscrit sur le totalisateur P; le diviseur I0I0, sur le chiffreur M; le quotient se forme dans le chiffreur X. Un régulateur règle la suite des opèrations. En outre, un chiffreur à un élément contenant la constante 1 est nécessaire.

(1): Le régulateur commande le transfert de M à Ov.

(2): Le régulateur commande le transfert de Ov à P, et, simultanément le deplacement de M et X, comme dans la multiplication.

(3): Le chiffre 0 dans le chiffreur de signe de P commande, simultanément le transfert de I à X, et le transfert de M à Ov. (Si le chiffre du chiffreur de signe de P est I, cette commande n'a pas lieu).

(4) Le régulateur commande le déplacement de M et X, et le chiffre O du chiffreur de signe de P commande le transfert de Ov à P. (Si le chiffre du chiffreur de signe de P est I, c'est le transfert de M à P qui est commandé).

(5) Le nombre qui apparaît sur P est formé seulement de chiffres I, sans qu'il y ait de report sans fin. On rencontre là un cas exceptionnel; si l'on ajoute I à ce nombre, le résultat obtenu est I, à cause du report sans fin: il faut donc considérer ce nombre comme égal à zero. La présence du chiffre I dans le chiffreur de signe justifie de lui donner le nom de zéro négatif.

Le zéro négatif commande le transfert de I à X. Mais il ne commande pas de transfert de M ou de Ov à P (contrairement aux temps 3 et 4). Ensuite:(7): Le régulateur commande le déplacement de X et M.

(8): Le régulateur arrête l'opération.

On voit que la division s'effectue dans le même temps que la multiplication, ce qui constitue un avantage considérable.

Elle nécessite, en plus des dispositifs nécessités par la multiplication:

On remarquera enfin que, pour utiliser complétement, le totalisateur P, il faut ajouter un élément à la droite de M.

Sans détailler le processus des opérations d'extraction de la racine carrée, nous dirons que:

L'extraction d'une racine carrée se ramène à une suite d'additions et de soustractions analogues à celles qui constituent une division.

Aucun nouveau chiffreur n'est nécessaire.

Des commandes conditionnelles nouvelles sont nécessaires.

Le calcul en parallèle permet donc de simplifier considérablement le processus de la division et de la racine carrée, mais le paraît nécessiter des organes assez nombreux:

Nous allons voir que les dispositifs peuvent être réalisés avec une grande simplicité.

Nous noterons particulièrement que plusieurs commandes conditionnelles ne peuvent pas être réduites à la forme: entraîne l'operation (A), entraîne l'operation (B).

Cette particularité paraît propre aux machines parallèles.

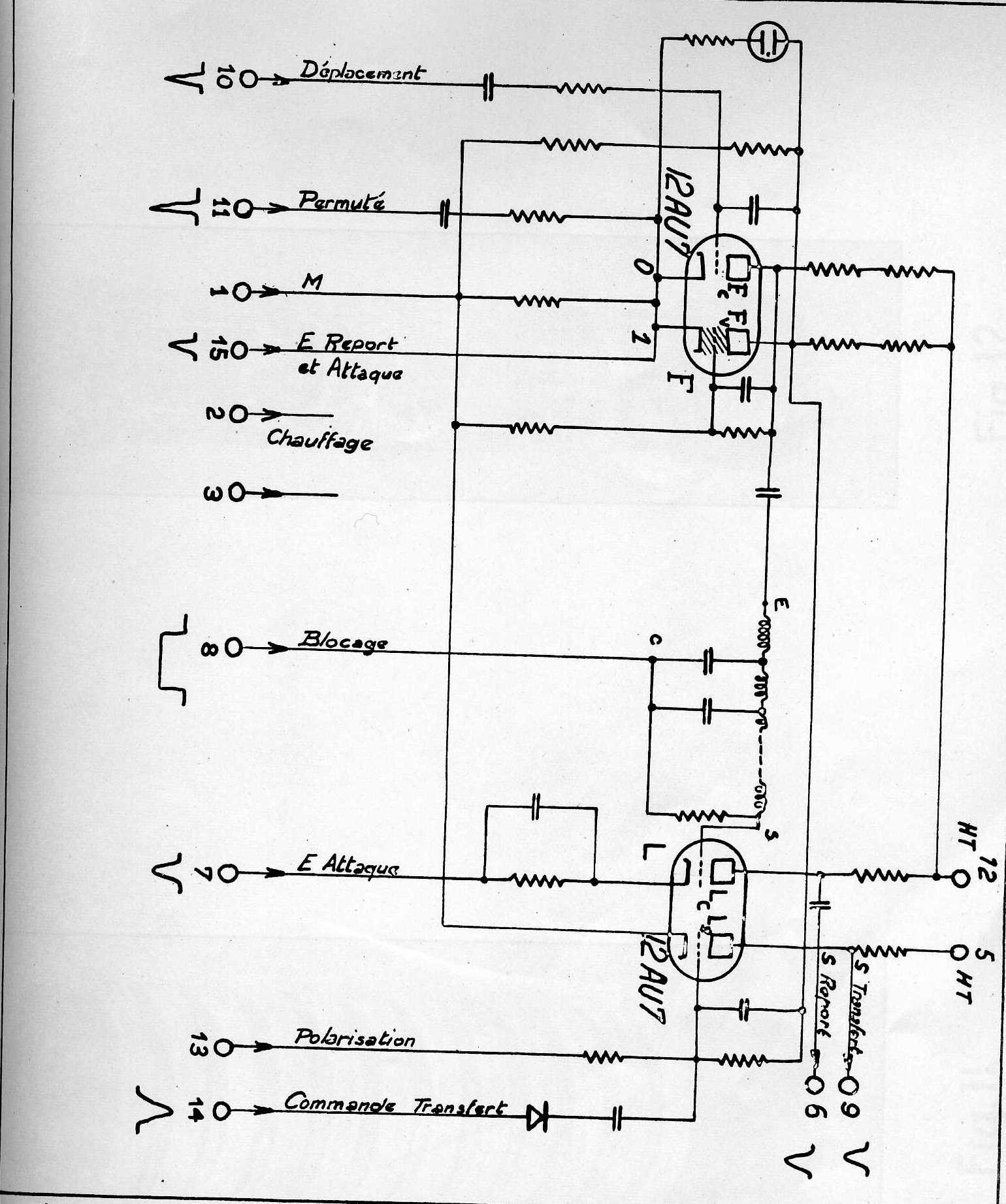

La figure 10 montre le schéma d'un élément de totalisateur correspondent à un ordre binaire.

Les liaisons entre les divers étages s'établissent comme suit:

La double-triode de gauche, F, montée en flip-flop, constitue l'élément de chiffrage: la triode de gauche du groupe représente I ou 0 selon qu'elle débite ou non. Nous l'appellerons triode de chiffrage; nous appellerons l'autre triode de verrouillage (lock triode).

[3] L'inscription d'un chiffre s'effectue en agissant sur la borne 7 qui, à travers la triode de gauche, Le, de la seconde double-triode, L, la borne 6 et la borne 15 de l'étage suivant, agit sur le flip-flop de cet étage.

Nous appellerons la triode de gauche de la seconde double-triode une triode d'entrée (input triode).

Le transfert d'un nombre s'effectue per la triode de droite, Le, de la double triode L. Nous l'appellerons triode de sortie (output triode). Cette triode est, normalement, au dessous du cut-off. Elle est près du cut-off quand le flip-flop F marque I, la triode de verrouillage ayant sa plaque à la tension haute. Une impulsion positive, donnée par la borne 14, peut alors traverser la triode de sortie Ls et sortir par la borne 9,

Le report s'effectue par la ligne de retard ES. Les chiffres des divers étages binaires sont inscrits simultanément. Quand cette inscription fait passer le flip-flop F de I à 0, l'impulsion positive qui en résulte pour la triode Fc traverse la ligne de retard et, à travers la triode d'entrée, Le, agit comme l'impulsion du plot 7 ([3]); cette impulsion atteint le flip-flop suivant après que celui-ci a achevé le basculement que peut avoir provoqué l'inscription directe du chiffre qui le concerne.

Le déplacement d'un nombre de droite à gauche sur un chiffreur est identique à l'addition de ce nombre a lui-même.

Si l'on envoie une impulsion négative sur la grille de la triode Fc, par la borne 10, rien ne se produit si la triode ne débite pas, et elle change d'état si elle débite; elle passe alors de I à 0, ce qui produit le même effet que si l'on avait ajouté I par la voie normale d'inscription (borne 7). On a donc ajouté le nombre à lui-même.

Pour déplacer un nombre de gauche à droite, il suffit de monter les lignes de retard en sens contraire.

En envoyant une impulsion sur tous les flip-flops à la fois, par la borne 11, on les fait basculer; il suffit de bloquer les lignes de retard en envoyant une impulsion négative d'assez longue durée par la borne 8, pour qu'il ne se passe pas autre chose que le basculement des flip-flops.

En consequence, un totalisateur ainsi construit est son propre overdraft. On peut remarquer que le sens du report est sans importance, puisque le report est bloqué pendant la permutation.

Le déplacement combiné avec le bloquage des reports donne l'effaçage.

Le systeme représenté par le schéma de la fig. 10 permet donc de réaliser toutes les fonctions que nous avons reconnues nécessaires à un totalisateur algébrique parallèle.

Il se réduit à deux double-triodes miniatures, une dizaine de résistances, une vingtaine de capacités, et la ligne de retard. La lampe à néon NE2 sert à visualiser le nombre inscrit: elle est allumée quand le flip-flop marque I.

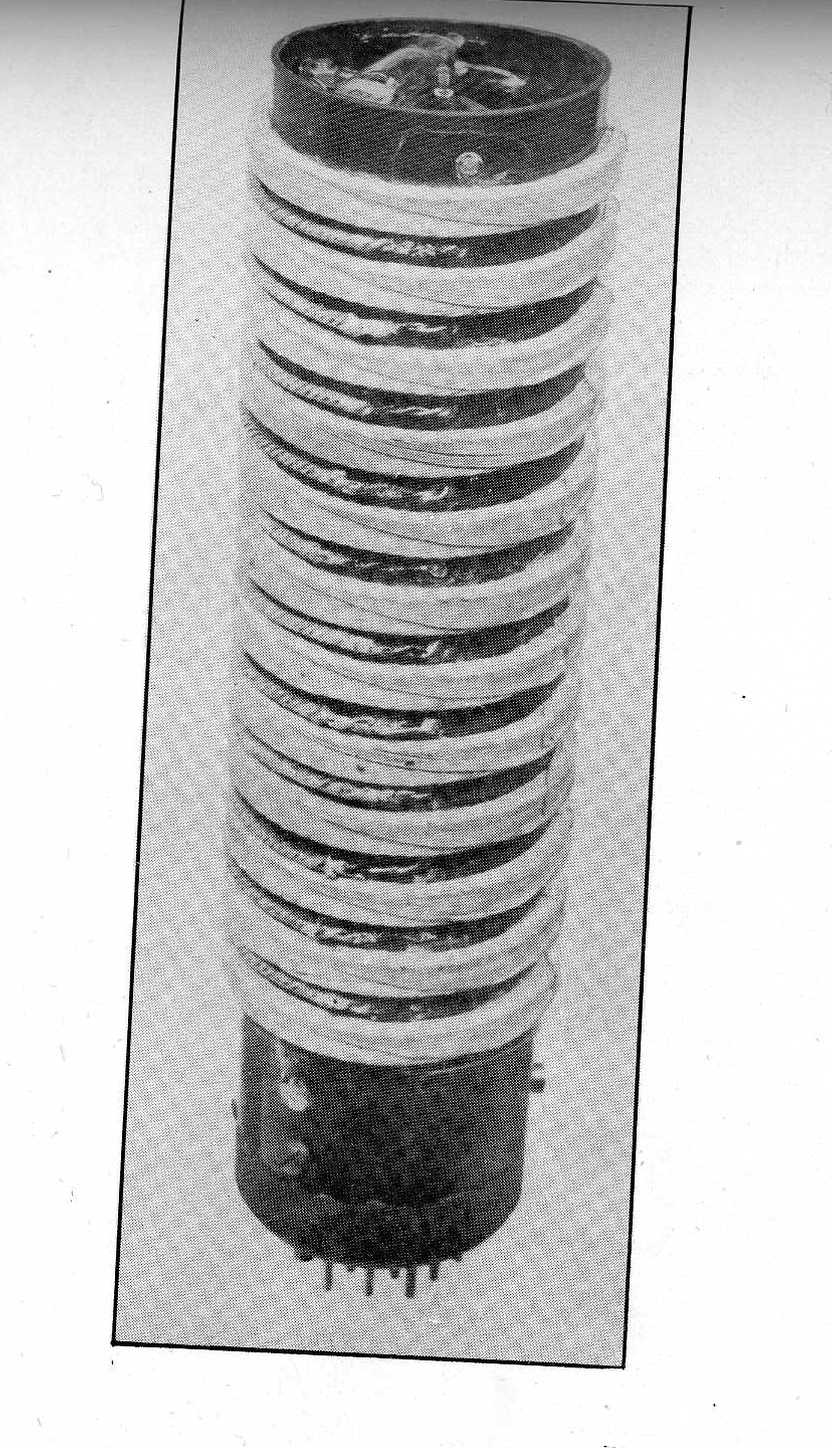

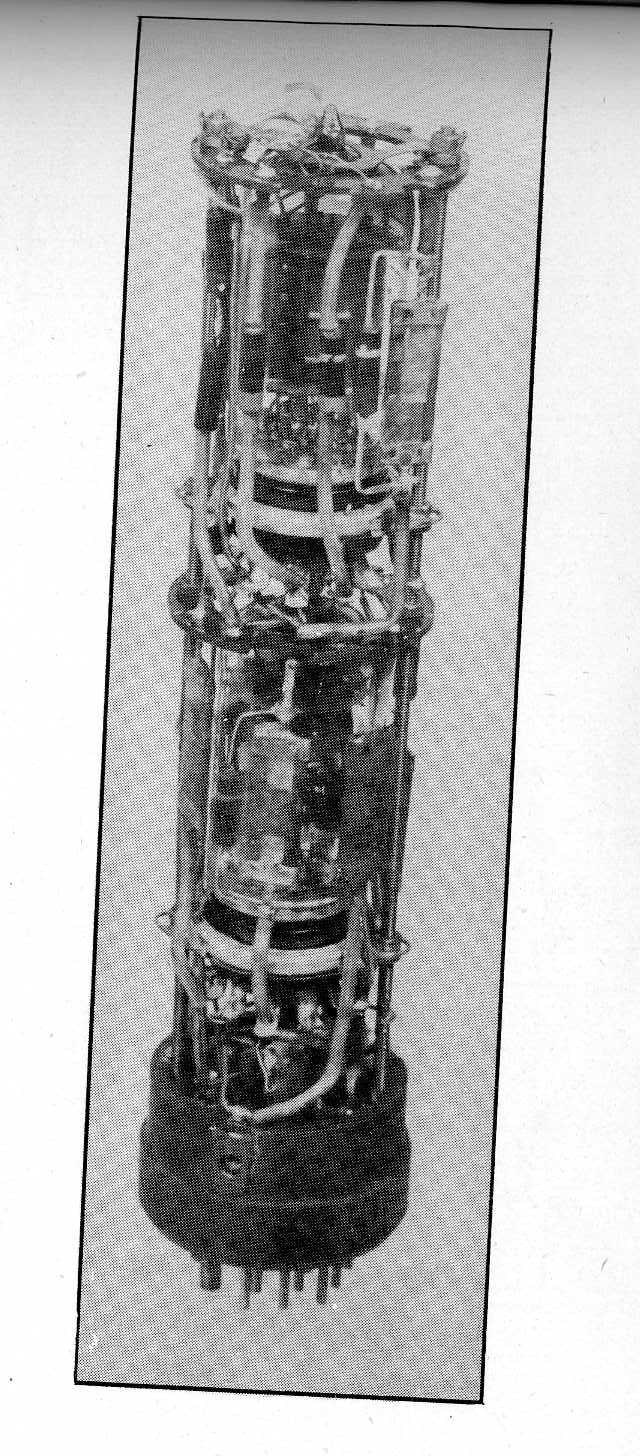

La fig. 11 montre la réalisation adoptée pour cet ensemble, non compris la ligne de retard.

La ligne de retard est bobinée sur un tube de carton fort qui sert de carter au montage de la fig. 11. Les contacts qui sont à la base de la ligne de retard assurent, par frottement, l'emboîtement du tube de carton sur le socle du montage. La fig. 12 montre cet ensemble.

Le socle s'engage sur une embase qui sera fixée sur un bâti supportant tous les éléments d'un même totalisateur, L'échange standard des éléments endommagés est ainsi assuré.

Le bâti est constitué par une boîte à vent, dans laquelle est soufflé de l'air comprimé qui, par un trou percé dans le socle de chaque élément, circule autour des tubes thermioniques et en assure le refroidissement.

Nous appelons calculatrice complète, un ensemble capable d'effectuer les opérations suivantes: addition, subtraction, multiplication, division, racine carrée, sur des nombres algébriques.

Il résulte des sections 1 et 2 ci-dessus qu'une calculatrice peut être constitutée comme suit pour une capacité de k chiffres binaires:

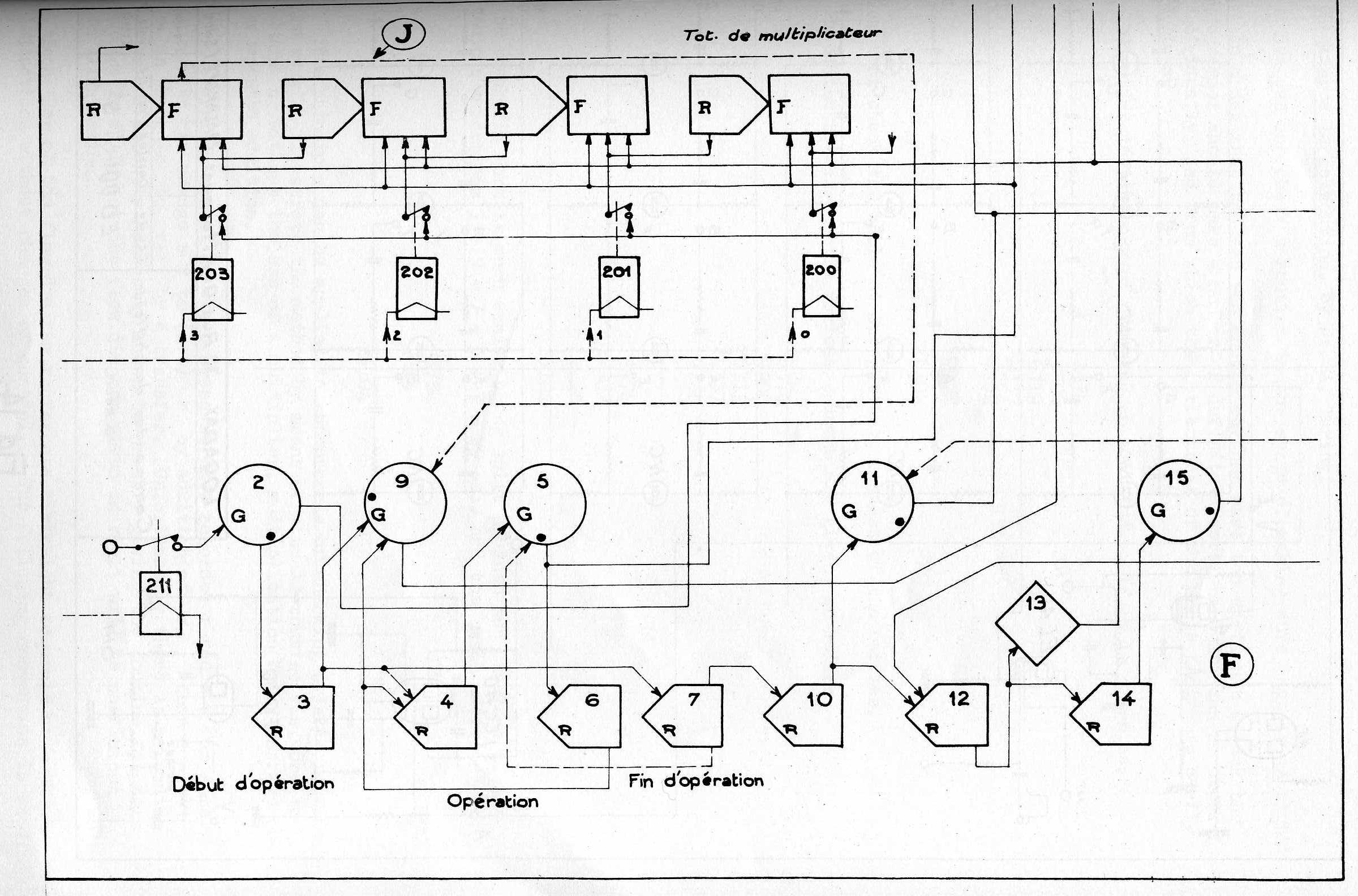

A titre d'indication, la fig. 13 montre le régulateur de la multiplication. (Les tubes No. 10 à 15 sont relatifs à des commandes différentes).

L'opération est déclanchée par le relai 211, qui déclanche le générateur d'impulsion 2.

Ce dernier commande:

[4] Le retard du tube 3 est égal a la durée d'inscription du multiplicande sur M. A la fin de cette. inscription, le tube 3 :

[6] Le générateur 9 lance une impulsion dans le premier élément du multiplicateur X, qui le traverse s'il marque I et, dans ce cas, déclanche le transfert de M à P.

A la fin de ce transfert, le tube de retard 4 déclanche le générateur d'impulsion 5; ce générateur, normalement bloqué statiquement par 7, est débloqué, du fait que 7 à été commandé par 3 ([5]).

Le générateur 5 commande:

[7] A la fin du déplacement de X et M, le tube de retard 6 déclanche 9 et 4, comme l'a fait 3 ([4]).

Le cycle des opérations [6] à [7] se répète jusqu'a la fin de la multiplication. A ce moment, le tube 7 bloque statiquement le générateur 5 et l'operation [7] n'a pas lieu.

Comme on le voit, quelques tubes suffisent pour assurer les commandes d'opérations.

(On notera que les temps de retard marqués sur la figure se rapportent à des totalisateurs construits avec des tubes plus lents que les tubes 12AU7 de la fig. 12).

Au total, pour une capacité de 15 chiffres décimaux, une calculatrice complète nécessite environ 500 tubes 12AU7, 250 tubes néon et 50 tubes de commande de types divers. Elle peut être montée toute entière et sur un rack standard.

Nous avons déjà montré que quelques chiffreurs de réserve suffisent pour permettre à une calculatrice complète de calculer automatiquement un polynôme à un nombre quelconque de variables (les données étant fournies, bien entendu, par une mémoire externe).

On peut, dans ces conditions, constituer cette mémoire par des tubes à vide.

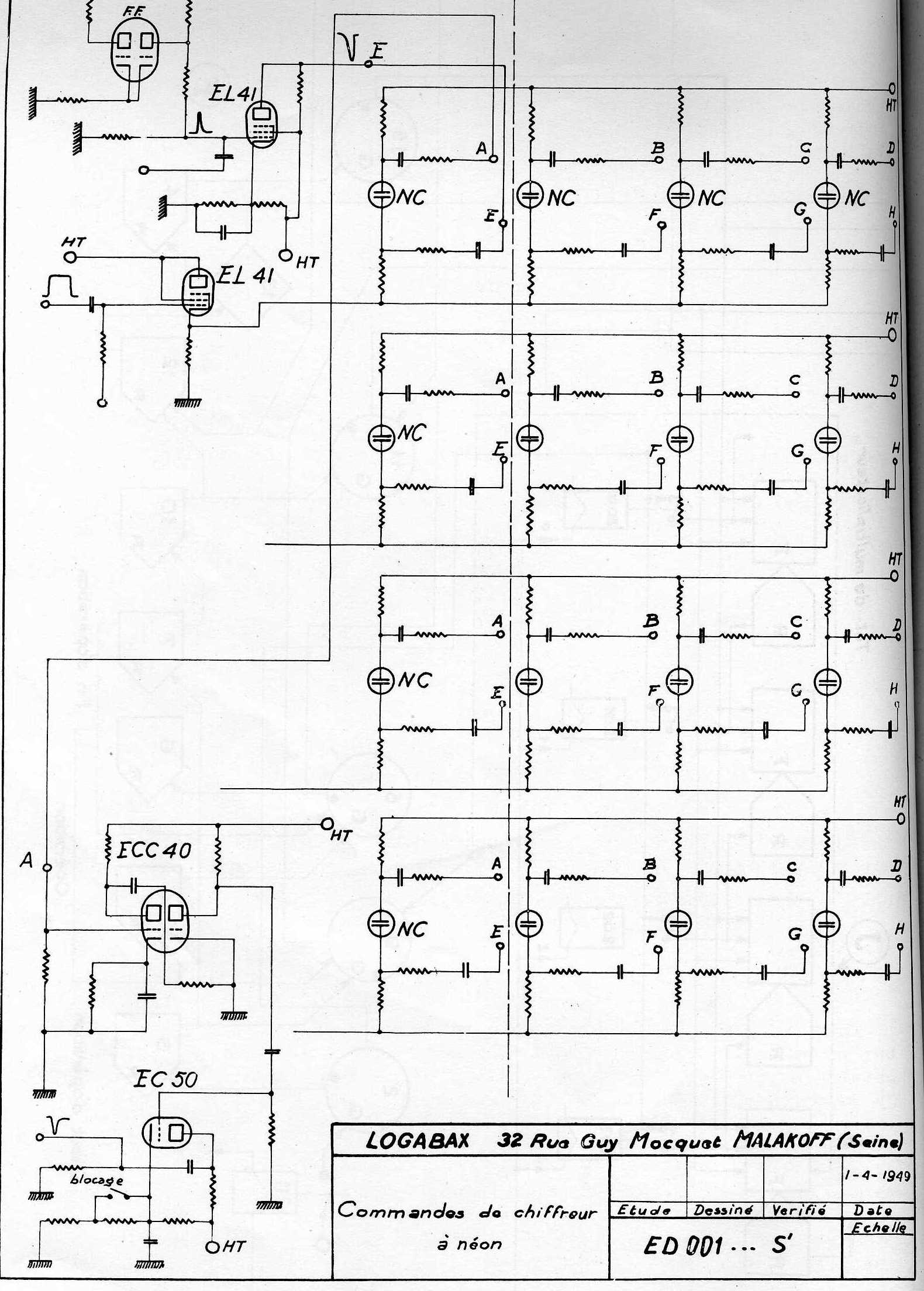

La fig. 14 montre le schéma d'une mémoire où les éléments de chiffreurs sent constitués par des. diodes à gas.

Les idées directrices relatives au montage et à la commande de ce dispositif sont celles qui viennent d'être exposées au sujet da la calculatrices complète.

Les diodes d'une même ligne horizontale représentent les chiffres d'un même nombre; les diodes d'une même ligne verticale représentent les chiffres d'un même ordre binaire.

Les bornes affectées de la même lettre sont reliées par un fil commun.

Le fonctionnement repose sur les remarques suivantes:

Les impulsions d'inscription, de lecture ou d'effaçage sont envoyées sur toutes les diodes d'un même ordre binaire simultanément. La sélection du chiffreur sur lequel elles doivent agir se fait en appliquant des impulsions compensatrices aux autres chiffreurs.

Pour effectuer les commandes, il suffit d'une ou deux lampes par rangée verticale ou horizontale de diodes, quel que soit le nombre de diodes. Le dispositif est donc, dans son ensemble, fort économique.

La durée de la lecture d'un nombre est de quelques micro secondes (4 à 8 selon le type de diodes utilisé). Cette durée très brève peut avoir pour conséquence une réduction appréciable du temps de calcul.

In answer to questions, Monsieur L. Couffignal said, referring to the selection of neon tubes, that 1 in 10 of the first kind used had been suitable, but they had only had to reject 1 in 50 of the new kind supplied by the G.E.C. The delay is 2 microsecs. This is the time taken to change the flip-flop. It is necessary to wait before all the carry-overs are finished. It had not yet been decided in what order the orders would be held in the machine, but there would probably be two different memories. The machine was still under development. The internal memory could store 100 numbers which had proved to be sufficient. The capacity of the external memory was indefinite. Only a few places are necessary in the memory to store orders and these are treated as numbers.

Mr. Wilkes thanked Monsieur Couffignal and congratulated him upon the progress made.